Hitachi, Ltd. (TSE: 6501) today announced the HM5212325FBPC 128-Mbit synchronous

DRAM (SDRAM), featuring a x32-bit configuration and small size, for use as buffer

memory or main memory in digital still cameras and similar portable digital products.

Sample shipments will begin in May 2000 in Japan.

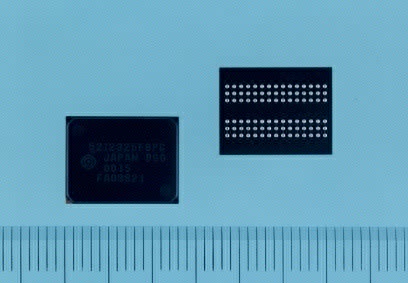

In the HM5212325FBPC, a x32-bit configuration is achieved by mounting two Hitachi 64-

Mbit SDRAMs, ranking among the world's smallest, in an MC-FBGA*1 package-a newly

developed small, thin BGA package of Hitachi. As well as providing compatibility with a

32-bit system bus width, this has also reduced the area to approximately half that of a

standard TSOP package, offering space saving in the end product.

With the rapid growth of the market for digital still cameras, PDAs, and other portable

digital products in recent years, the capacity of the SDRAMs incorporated in such products

has also increased to 16 or 32 Mbytes. At the same time, the advent of a 32-bit system bus

width means that at least two x16-bit-configuration SDRAMs or four x8-bit-configuration

SDRAMs must be used per system.

Against this backdrop, Hitachi already developed a "multi chip package" with a number of

LSI chips mounted in a single package, and released x64- and x32-bit-configuration 256-

Mbit SDRAMs with four 64-Mbit SDRAMs mounted in a BGA package, and also a x32-

bit-configuration 128-Mbit SDRAM with two 64-Mbit SDRAMs mounted in a BGA

package in June 1999. These devices have proved popular in the portable digital product

and telecommunication product markets. However, in portable digital applications such as

digital still cameras where portability is of prime importance, demand has grown for still

smaller and thinner packages.

In response to this demand, Hitachi has now developed the HM5212325FBPC 128-Mbit

SDRAM, offering a x32-bit configuration in approximately half the area of a TSOP

package.

The newly developed MC-FBGA package has been made smaller and thinner, with

dimensions of 10.0 mm x 13.0 mm x 1.45 mm (max.), through the use of new techniques

such as reducing the PCB(Printed Circuit Board) thickness. With two Hitachi 64-Mbit

SDRAM chips mounted to achieve a x32-bit configuration, a single HM5212325FBPC can

provide a memory system with a 32-bit bus width and a 16M-byte (128-Mbit) capacity

suitable for digital still cameras and similar products. As a similar memory system

configured with conventional TSOP packages requires two 64-Mbit SDRAMs (x16), use of

the HM5212325FBPC enables system size to be reduced to approximately 1/4 by area and

1/3 by volume. In addition, for applications requiring product expansion to a larger

capacity of 256 Mbits, providing a two-package footprint in advance will allow a 256-Mbit

(x32 or x64) capacity to be achieved in virtually the same space as a single TSOP.

The power supply voltage is 3.3 V, for PC100 compatibility. The package conforms to the

JEDEC standard 90-pin BGA package, with a 0.8 mm ball pitch and 0.45 mm ball diameter.

Unlike current CSP packages*2, the silicon surface of the chip is not exposed, allowing

easier handling.

Future plans include the development of high-speed products, including PC133-compatible

models, as well as low current specification and 2.5 V operation products. Extension of the

multichip package SDRAM series will also continue, including the development of large-

capacity 512-Mbit models.

Notes:1.MC-FBGA: Multi Chip Fine Pitch Ball Grid Array. A BGA (Ball Grid Array) is a type of

package in which solder balls are arranged in array form on the PCB surface as

input/output pins.

2.CSP: Chip Size (or Scale) Package

< Typical Applications >

Buffer memory and main memory in portable digital products such as digital still cameras

and PDAs

< Price in Japan > (For Reference)

Product Code Sample Price (Yen)

HM5212325FBPC 4,500

< Specifications >

Part Number HM5212325FBPC

Memory capacity 128 Mbits

Bit configuration x32

Bank configuration 4 banks

Operating voltage 3.3 ±0.3 V

Operating speed PC100 (CL3)

Operating current 110 mA

Standby current 4 mA

Package JEDEC standard 90-pin BGA

Package dimensions 10.0 mm x 13.0 mm x 1.45 mm (max)

|