Hitachi, Ltd. (TSE: 6501) today announced the development of the new LFPAK (Hitachi package

code name)thin package that achieves an ultra-low on-resistance*1 and low thermal resistance

for a power MOS FETthrough the use of bonding-wire-less construction, for use in small power

supplies for portable devices such as notebook PCs, and communication products in Japan.

The new package enables on-resistance to be reduced by 20% compared with the JEDEC standard

SOP-8 small, thin package, making it possible to realize a power MOS FET with a low

on-resistance of 2.3 m ohm(typ) at a 30 V withstand voltage when Hitachi's latest 0.5 ¦Ìm

power MOS FET process*2 is used.

As the initial power MOS FET employing this package, Hitachi is now releasing the HAT2096H

offering the industry's lowest on-resistance of 4.2 m ohm (typ) at a 30 V withstand voltage.

Sample shipments will begin in July 2000.

To meet the demand for smaller size, lighter weight, and higher efficiency, Hitachi currently

mass-produces power MOS FETs that offer improvements in the chips themselves and employ a small

SOP-8 package (external dimensions: 5.0 mm x 6.2 mm x 1.75 mm (max)). However, in order to

achieve the small size, light weight, and long operating time demanded of portable devices using

batteries as their main power supply, and the small size and high efficiency demanded of

communication products, there is a growing demand for the power MOS FETs that control power in

these products to offer significantly lower on-resistance together with high-speed operation,

lower noise, smaller and lighter construction, and lower thermal resistance.

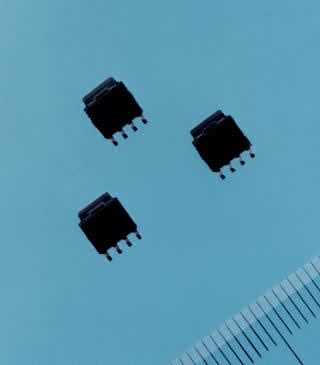

It was against this backdrop that Hitachi developed the new LFPAK package, featuring a thickness

of only 1.1 mm while retaining the same on-board footprint as an SOP-8 package, that enables

on-resistance to be cut by approximately 20%.

By eliminating the conventionally used bonding wire, and instead bonding the semiconductor

electrode plates comprising the pins directly to the silicon chip, this new package succeeds

in minimizing to the ultimate degree the resistance component and impedance attributable to

the wire (loss-free design), while at the same time achieving a thinner shape. In addition,

the use of a structure in which the drain pins are exposed on the rear surface of the package,

unlike the SOP-8 package, offers a significant improvement in thermal resistance.

As the initial product, the HAT2096H is an N-channel power MOS FET containing a chip employing

Hitachi's latest 0.5 ¦Ìm power MOS FET process with features of low on-resistance and

high-speed operation, and achieving the industry's lowest on-resistance of 4.2 m ohm (typ) at

a 30 V withstand voltage. The HAT2096H will make it possible to reduce the size and power

consumption of the CPU power supply circuit in notebook PCs and the power supply unit in

communication devices.

Moreover, when a power MOS FET employing the 0.5 um process-the largest size that can be used

in the LPAK package-is mounted, it is possible to attain an ultra-low on-resistance of2.3 m ohm

(typ).Embossed taping packaging is available as the standard delivery form, suitable for use in

automatic mounters.

Future plans include the release of a model with an ultra-low on-resistance of 2.3 m ohm (typ),

and the provision of a comprehensive product lineup with the development of series offering

products ranging from 20 V to 40 V.

Notes: 1. On-resistance: The operating resistance when a power MOS FET is operating.

This is the parameter that most affects the performance of a power MOS FET,

with a lower on-resistance resulting in higher performance.

2. 0.5 ¦Ìm power MOS FET process: Hitachi's 7th-generation power MOS FET process,

offering imultaneous improvements in on-resistance, input capacitance, and

switching speed.

< Typical Applications >

¢¡ CPU power supplies in notebook PCs, etc.

¢¡ Power supplies for communication devices (synchronous rectification)

< Prices in Japan > (For Reference)

Product Code Sample Price (Yen)

HAT2096H 350

< Specifications >

Values for Ta = 25°C

Maximum Ratings On-Resistance RDS(on)(mohm)

Product VDSS ID Pch

Code Package Type (V) (A) (W) VGS = 10 V GS = 4.5 V

HAT2096HLFPAK N-channel FET 30 40 20* 4.2 (typ) 6.2 (typ)

Note: * Value for Tc = 25°C

|