|

||

| “Three-Layer Stacked HJ931 Series” System in Package (SiP) with SuperHTM Microprocessor |

| — HJ931201BP incorporating microprocessor, flash memory, and synchronous DRAM in a single package reduces mounting area by approximately 65%— | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

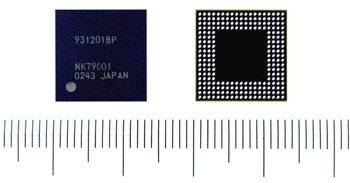

Tokyo, December 4, 2002— Hitachi, Ltd. (TSE: 6501) today announced the development of the "Three-layer stacked HJ931 Series" a "System in Package" (SiP) product incorporating a high-performance Hitachi SuperHTM microprocessor*1 and multiple memory chips in a single package by using three-layer stack structure. Engineering sample shipments are scheduled to begin shipping in December 2002 in Japan. Samples of the first product in the new series, the HJ931201BP, will also commence shipping in December 2002 in Japan. The HJ931201BP incorporates the SH7705, which is built on the SH-3 CPU core designed for use in low-power devices, a 64 -Mbit synchronous DRAM (SDRAM), and a 16-Mbit flash memory. The series is intended for use in portable devices such as digital cameras and PDAs. In addition to combining a microprocessor and multiple memory chips, such as SDRAM or flash memory, in a single package, something that is normally difficult to accomplish by "System on Chip" (SoC), it employs a three-layer stacked SiP to dramatically reduce the mounting area required. The HJ931201BP, for example, combines three chips—the SH7705, 64 -Mbit SDRAM, and 16—Mbit flash memory-in a 13 mm × 13 mm package that is 1.7 mm (maximum) thick. This results in a reduction of approximately 65% in the mounting area, compared with a configuration using three packages. < Background > In recent years there has been increasing demand for more functionality and greater compactness in the market for digital consumer products, in particular portable devices such as digital video cameras, digital still cameras, and PDAs. This has increased the need for SoC products, in which a microprocessor or ASIC is combined with memory on a single chip, and SiP products. Demand for SiP products in particular is growing rapidly due to the advantages they offer over SoC products. These advantages include shorter development times, lower development costs, and ease of application to a wide variety of product requirements and rapidly changing market conditions. Hitachi already has some SiP (the term multi-chip module or MCM is also used) products in volume production. Examples include side-by-side SiP and two-layer stacked SiP products incorporating a SuperH microprocessor and SDRAM or flash memory or memory and a custom ASIC. The new "Three-layer stacked HJ931 Series" achieves a smaller size by stacking its component chips in three-layers. < About this product > The features of the "Three-layer stacked HJ931 Series" are described below.

The microprocessor used in the HJ931201BP is the SH7705, which is built on the SH-3 CPU core designed for use in low-power devices. It has a fast operating frequency of 133 MHz and a low internal logic operating voltage of 1.5 V. This makes it ideal for portable products such as PDAs that require high performance and low power consumption.

The package uses the LFBGA 240-pin configuration and contains a total of three chips: the SH7705, 64-Mbit SDRAM, and 16-Mbit flash memory. It uses a three-layer stacked structure to achieve a size of 13 mm × 13 mm and a thickness of 1.7 mm (maximum). Hitachi plans to expand its series of "Three-layer stacked SiP" to include products with more than three chips as well as products containing custom ASIC chips. There are also plans for future upgrades to microprocessors with faster operating frequencies, etc. < Development Tools > The E10A card emulator is also available as a support tool for designing systems incorporating the "Three-layer stacked HJ931 Series".

|

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Information contained in this news release is current as of the date of the press announcement, but may be subject to change without prior notice. |

| WRITTEN BY Corporate Communications Division |